# N32G05x Series Errata Manual

# **Content**

| 1 | Err             | Errata List                                                                                 |   |  |  |

|---|-----------------|---------------------------------------------------------------------------------------------|---|--|--|

| 2 | Res             | et and clock control (RCC)                                                                  | 4 |  |  |

|   | 2.1             | HSE not fully started up, HSE_ready bit ready issue                                         | 4 |  |  |

|   | 2.2             | LSI ready bit ready issue                                                                   | 4 |  |  |

| 3 | Rea             | Гіme Clock(RTC)                                                                             |   |  |  |

|   | 3.1             | Tamper interrupt does not meet expectations                                                 | 4 |  |  |

| 4 | Ana             | alog to Digital Conversion(ADC)                                                             | 5 |  |  |

|   | 4.1             | When the ENDC flag is set, immediately read the ADC data register value for abnormal issues | 5 |  |  |

| 5 | Chi             | p Marking Information and Version Description                                               | 6 |  |  |

| 6 | Version history |                                                                                             |   |  |  |

| 7 | Not             | Notice                                                                                      |   |  |  |

### 1 Errata List

**Table 1-1 Errata Overview**

|                                                 | Errata link                                                                                              |   |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|---|--|--|--|

| chapter 2: Reset and clock                      | chapter 2.1: HSE not fully started up, HSE_ready bit ready issue                                         | • |  |  |  |

| control (RCC)                                   | chapter 2.2: LSI ready bit ready issue                                                                   | • |  |  |  |

| chapter 3: Real Time<br>Clock(RTC)              | chapter 3.1: Tamper interrupt does not meet expectations                                                 | • |  |  |  |

| chapter 4: Analog to Digital<br>Conversion(ADC) | chapter 4.1: When the ENDC flag is set, immediately read the ADC data register value for abnormal issues | • |  |  |  |

- •: There is this issue

- -: There is no such issue

### 2 Reset and clock control (RCC)

### 2.1 HSE not fully started up, HSE\_ready bit ready issue

### **Description**

After enabling HSE, HSE did not fully vibrate, but HSE READY was set.

#### **Solution**

1. Capture the HSE/128 clock using TIM2\_CH4, determine that HSE is fully oscillating, and add this code to the SDK. The maximum waiting time for determining whether HSE has fully started oscillating is 200ms. If it exceeds 200ms, HSI will be used as the system clock.

### 2.2 LSI ready bit ready issue

#### **Description**

The LSI ready bit cannot clear the issue in RUN mode.

#### Reason

1. In RUN mode, the LSI remains in the enabled state, the LSI enable bit is invalid, and the LSI remains in the ready state.

# 3 Real Time Clock(RTC)

### 3.1 Tamper interrupt does not meet expectations

#### **Description**

RTC intrusion pin rising/falling edge triggering tamper interrupt does not meet expectations, and there may be situations where it cannot be triggered or triggered incorrectly.

#### **Solution**

The RTC intrusion pin requires adding up/down resistors to the outer board level circuit.

### 4 Analog to Digital Conversion(ADC)

# 4.1 When the ENDC flag is set, immediately read the ADC data register value for abnormal issues

### **Description**

After ENDC is set, immediately read the ADC data register, which may read the result of the previous conversion.

#### **Solution**

- 1. After the ENDC flag is set, delay by 8 ADC\_CK clocks before reading the ADC data register;

- 2. In some scenarios, the ENDCA flag is used instead of the ENDC flag.

Email: sales@nsing.com.sg

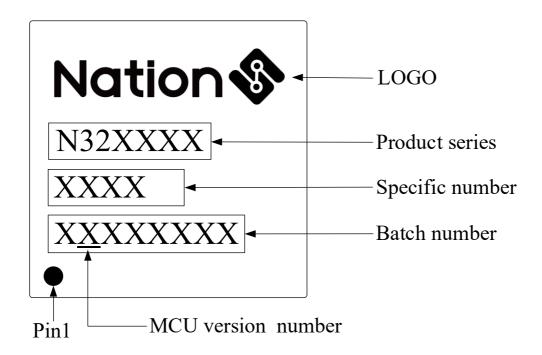

# 5 Chip Marking Information and Version Description

# 6 Version history

| Version | Data       | Changes                       |

|---------|------------|-------------------------------|

| V1.0.0  | 2024.7.18  | Initial version               |

| V1.1.0  | 2024.11.29 | 1. Update marking information |

### **Disclaimer**

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to Nations Technologies Inc. and Nations Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only.

NSING reserves the right to make changes, corrections, enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NATIONS has attempted to provide accurate and reliable information, NATIONS assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NATIONS be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product.

NATIONS Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NATIONS and hold NATIONS harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NATIONS, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.

Email: sales@nsing.com.sg